# PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

This manual supports the following TEKTRONIX products:

Factory Field

Installed Installed

Product Option Option

8550 1A 8300A01

MICROCOMPUTER

DEVELOPMENT LAB

8080A/8085A

ASSEMBLER SPECIFICS

USERS MANUAL

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

Serial Number \_\_\_\_\_

First Printing SEP 1980 Revised APR 1981

#### LIMITED RIGHTS LEGEND

| ise No |       |

|--------|-------|

|        | se No |

Contractor: Tektronix, Inc.

Explanation of Limited Rights Data Identification Method

Used: Entire document subject to limited rights.

Those portions of this technical data indicated as limited rights data shall not, without the written permission of the above Tektronix, be either (a) used, released or disclosed in whole or in part outside the Customer, (b) used in whole or in part by the Customer for manufacture or, in the case of computer software documentation, for preparing the same or similar computer software, or (c) used by a party other than the Customer, except for: (i) emergency repair or overhaul work only, by or for the Customer, where the item or process concerned is not otherwise reasonably available to enable timely performance of the work, provided that the release or disclosure hereof outside the Customer shall be made subject to a prohibition against further use, release or disclosure; or (ii) release to a foreign government, as the interest of the United States may require, only for information or evaluation within such government or for emergency repair or overhaul work by or for such government under the conditions of (i) above. This legend, together with the indications of the portions of this data which are subject to such limitations shall be included on any reproduction hereof which includes any part of the portions subject to such limitations.

#### RESTRICTED RIGHTS IN SOFTWARF

The software described in this document is licensed software and subject to **restricted rights**. The software may be used with the computer for which or with which it was acquired. The software may be used with a backup computer if the computer for which or with which it was acquired is inoperative. The software may be copied for archive or backup purposes. The software may be modified or combined with other software, subject to the provision that those portions of the derivative software incorporating restricted rights software are subject to the same restricted rights.

Copyright © 1980 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and are registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

# Section 12A 8080A/8085A ASSEMBLER SPECIFICS

|                                                                                                     | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Demo                                                                                                | nstration Run12A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16-Bit<br>8-Bit<br>Status                                                                           | ecture       12A-1         Registers       12A-1         Registers       12A-2         Register       12A-3         ssing Modes       12A-4                                                                                                                                                                                                                                                                                                                                                         |

| Notat                                                                                               | onal Conventions12A-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Jumps<br>Stack<br>Subroi<br>Subroi<br>Data<br>Arithm<br>Logica<br>Misce<br>Instruc<br>Resen<br>Page | ction Set       12A-9         12A-9       12A-10         Operations       12A-10         utine Handling: Calls       12A-10         utine Handling: Returns       12A-11         Transfer       12A-12         netic Operations       12A-13         I Operations       12A-15         Ilaneous (IN, OUT, HLT, NOP, Interrupt Instructions)       12A-15         ctions Available On 8085A Only       12A-18         yed Words       12A-19         Size       12A-20         larities       12A-20 |

|                                                                                                     | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>Table</b><br><b>No</b> .<br>12A-1<br>12A-2                                                       | Register Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                     | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Fig.<br>No.<br>12A-1                                                                                | The 8080A/8085A Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12A-2                                                                                               | Stack Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

@

| INDEX OF 8080A/8085A MNEMONICS                      | Page    |

|-----------------------------------------------------|---------|

| ACI—Add immediate byte to accumulator with carry    | •       |

| ADC—Add source to accumulator with carry            |         |

| ADD—Add source to accumulator with no carry         |         |

| ADI—Add immediate byte to accumulator with no carry | 12A-13  |

| ANA—AND accumulator with source                     | 12A-15  |

| ANI—AND accumulator with immediate byte             | 12A-15  |

| CALL—Call subroutine unconditionally                | 12A-10  |

| CC—Call if carry set                                | 12A-10  |

| CM—Call if minus                                    | 12A-10  |

| CMA—Complement accumulator                          | 12A-15  |

| CMC—Complement carry flag                           | 12A-16  |

| CMP—Compare accumulator with source                 | 12A-15  |

| CNC—Call if carry not set                           | 12A-10  |

| CNZ—Call if not zero                                | 12A-10  |

| CP—Call if plus                                     | 12A-10  |

| CPE—Call if parity even                             | 12A-11  |

| CPI—Compare accumulator with immediate byte         | 12A-16  |

| CPO—Call if parity odd                              | 12A-11  |

| CZ—Call if zero                                     | 12A-10  |

| DAA—Decimal adjust accumulator                      | 12A-14  |

| DAD—Dual addition of register pairs                 | 12A-13  |

| DCR—Decrement 8-bit register                        | 12A-14  |

| DCX—Decrement register pair                         | 12A-14  |

| DI—Disable interrupts                               | 12A-17  |

| EI—Enable interrupts                                | 12A-17  |

| HLT—Halt processor                                  | 12A-17  |

| IN—Send in byte from device to accumulator          | 12A-17  |

| INR—Increment 8-bit register                        | 12A-14  |

| INX—Increment register pair                         | 12A-14  |

| JC—Jump if carry set                                |         |

| JM—Jump if minus                                    |         |

| JMP—Jump unconditionally                            |         |

| JNCJump if carry not set                            |         |

| JNZ—Jump if not zero                                | . 12A-9 |

12A-ii

|                                                          | Page   |

|----------------------------------------------------------|--------|

| JP—Jump if plus                                          | 12A-9  |

| JPE—Jump if parity even                                  |        |

| JPO—Jump if parity odd                                   |        |

| JZ—Jump if zero                                          |        |

| LDA—Load accumulator with 8-bit register                 | 12A-12 |

| LDAX—Load accumulator with contents of register pair     |        |

| LHLD—Load H register pair with consecutive memory bytes  |        |

| LXI—Load register pair with immediate address            |        |

| MOV—Move source to destination                           |        |

| MVI—Move immediate source to destination                 |        |

| NOP—No operation                                         |        |

| ORA—OR accumulator with source                           |        |

| ORI—OR accumulator with immediate byte                   |        |

| OUT—Send byte from accumulator to device                 |        |

| PCHL—Load program counter with H register pair           |        |

| POP—Send top of stack to destination                     |        |

| PUSH—Send source to top of stack                         |        |

| RAL—Rotate accumulator left through carry                |        |

| RAR—Rotate accumulator right through carry               |        |

| RC—Return if carry set                                   |        |

| RET—Return unconditionally                               |        |

| RIM—Read interrupt mask                                  |        |

| RLC—Rotate accumulator left with carry affected          |        |

| RM—Return if minus                                       | 12A-11 |

| RNC—Return if carry not set                              | 12A-11 |

| RNZ—Return if not zero                                   | 12A-11 |

| RP—Return if plus                                        | 12A-11 |

| RPE—Return if parity even                                | 12A-11 |

| RPO—Return if parity odd                                 | 12A-11 |

| RRC—Rotate accumulator right with carry affected         | 12A-16 |

| RST—Restart at vectored subroutine                       | 12A-17 |

| RZ—Return if zero                                        | 12A-11 |

| SBB—Subtract source from accumulator with borrow         |        |

| SBI—Subtract immediate byte from accumulator with borrow | 12A-14 |

| SHID. Store H register pair in consectuve memory bytes   | 12Δ-12 |

|                                                             | Page     |

|-------------------------------------------------------------|----------|

| SIM—Set interrupt mask                                      | . 12A-18 |

| SPHL—Load stack pointer with H register pair                | 12A-10   |

| STA—Store accumulator at destination                        | 12A-12   |

| STAX—Store accumulator at register pair destination         | 12A-13   |

| STC—Set carry flag to one                                   |          |

| SUB—Subtract source from accumulator without borrow         |          |

| SUI—Subtract immediate byte from accumulator with no borrow |          |

| XCHG—Exchange register pairs                                |          |

| XRA—Exclusive OR accumulator with source                    |          |

| XRI—Exclusive OR accumulator with immediate byte            | 12A-15   |

| XTHL—Exchange top of stack with H register pair             | 12Δ-10   |

12A-iv

# Section 12A 8080A/8085A ASSEMBLER SPECIFICS

## **DEMONSTRATION RUN**

This Assembler Specifics section is intended as a supplement to the 8300AXX Assembler Users Manual. The Demonstration Run for the 8080A/8085A can be found in the Learning Guide of that manual.

### **ARCHITECTURE**

The 8080A/8085A is an 8-bit microprocessor with a 64K addressable memory space. Its architecture includes a control unit, an 8-bit bidirectional data bus, an 8-bit accumulator served by an Arithmetic Logic Unit (ALU), and a versatile set of internal 8-bit and 16-bit registers. The following paragraphs discuss those registers accessible to the user.

## 16-Bit Registers

There are three types of 16-bit registers: simple 16-bit register, register pair, and pseudo-register pair. Note that the generality of the 16-bit registers is limited; there are no instructions that apply to all six 16-bit registers. Table 12A-1 shows the organization of the 16-bit registers and their constituent 8-bit registers.

Table 12A-1 8080A/8085A Register Organization

| Name | 16-Bit Register Type | High-Order Byte | Low-Order Byte |

|------|----------------------|-----------------|----------------|

| PSW  | Pseudo-Register Pair | а               | status         |

| В    | Register Pair        | b               | С              |

| D    | Register Pair        | С               | d              |

| Н    | Register Pair        | h               | 1              |

| SP   | Simple 16-Bit        |                 |                |

| PC   | Simple 16-Bit        |                 |                |

In Table 12A-1, each of the first four 16-bit registers (**PSW**, **B**, **D**, and **H**) contains two separately addressable 8-bit registers. These 8-bit registers are labeled with lowercase letters. This 8-bit/16-bit duality provides for simple and efficient processing of addresses and their contents.

@ 12A-1

#### Simple 16-bit Registers: PC, SP

The program counter (**PC**) and the stack pointer (**SP**) are simple 16-bit registers and have no directly addressable single bytes. Only in a limited number of instructions may either of these registers be treated as a register pair.

#### Register Pairs: B, D, and H

The three register pairs are designated with the uppercase letters **B**, **D**, and **H**. They are **not** to be confused with the corresponding 8-bit registers **b**, **d**, and **h**. This uppercase/lowercase convention is used here for readability. In actual assembly language programming uppercase letters are used to designate both 8-bit and 16-bit registers. The instruction itself determines whether the uppercase letter represents an 8-bit or a 16-bit register.

Among the register pairs, the  ${\bf H}$  register pair has additional features: it is uniquely supported by the PCHL, SPHL, XTHL, XCHG, LHLD, and SHLD instructions. The  ${\bf H}$  register pair also holds the address of the memory byte  ${\bf M}$ .

#### Pseudo-Register Pairs: PSW

The Program Status Word (**PSW**) is classified as a pseudo-register pair because the accumulator and status register are distinct and separate 8-bit registers and have no logical connection. However, the POP and PUSH instructions treat the accumulator and status registers as if they are a register pair.

### The 8-Bit Registers

The individual 8-bit registers all exist as the high-order and low-order bytes of 16-bit registers. A discussion of the 8-bit registers follows.

#### The Accumulator

The accumulator (a) is uniquely supported by logical and arithmetic instructions because of its direct connection to the Arithmetic Logic Unit (ALU). The accumulator is also the first byte of the Program Status Word (PSW).

#### The Simple 8-Bit Registers

The simple 8-bit registers (**b**, **c**, **d**, **e**, **h**, and **l**) behave alike when addressed as 8-bit registers. The accumulator may be considered a member of this group although it is supported by additional arithmetic and logical instructions. The status register does not belong to this group and is discussed separately.

#### The Status Register

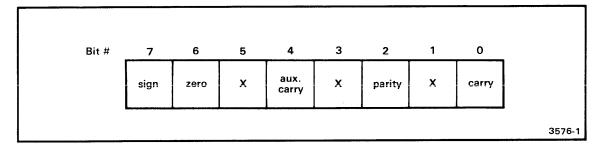

The 8-bit status register contains a sequence of flags which may be set by conditions generated from instruction operations. Figure 12A-1 shows the position of these flags within the status register.

Fig. 12A-1. The 8080A/8085A Status Register and its flags.

- Bit 0 The carry flag is set to 1 if either a carry or borrow occurs out of the accumulator during instruction execution.

- Bits 1,3,5 The values of bits 1, 3, and 5 vary depending on chip manufacturer and on whether the chip is an 8080A or 8085A. These bits are **not** written to during a POP PSW instruction.

- Bit 2 The parity flag is set to 1 if parity is even, and cleared to 0 if parity is odd. Parity is calculated from the sum of 1-valued bits in the accumulator. For instance, if the binary value in the accumulator is 00000011, then the sum of 1-valued bits is 2 and parity even.

- Bit 4 The auxiliary carry flag is used with Binary Coded Decimal (BCD) arithmetic. A BCD number requires only a 4-bit representation; thus two BCD digits may be stored in a byte. The auxiliary carry flag is set to 1 if either a carry or a borrow occurs between BCD numbers within that byte.

- Bit 6 The zero flag is set to 1 when an operation results in 0.

- Bit 7 The **sign flag** is set to 1 when an operation results in a two's-complement negative number with the seventh bit a 1.

The carry and auxiliary carry flags are inconsistently implemented for several instructions. For instance, the INR and DCR instructions affect all status flags except the carry flag, while the INX and DCX instructions affect no flags whatsoever. Flag settings differ for the 8080A and 8085A as well. For example, the auxiliary carry settings for the ANI and ANA are processor dependent. The description of the instruction set in this section describes these differences in detail.

### ADDRESSING MODES

The following addressing modes are used by the 8080A/8085A.

#### Immediate Addressing

In immediate addressing, the explicit value of the instruction operand is the value on which the instruction operates.

# **Direct Addressing**

In direct addressing, the instruction operand is a register or address containing the value on which the instruction operates.

## Indirect Addressing

The 8080A/8085A supports a form of indirect addressing in which the instruction operand  $\mathbf{M}$ , designates a memory byte on which the instruction operates. Note that  $\mathbf{M}$  is indirectly addressed by  $\mathbf{H}$  in this addressing mode.

## Implied Addressing

In implied addressing, the operand is implicitly specified by the instruction; there is no explicit instruction operand. For example, the RAL instruction has no operands, since the accumulator is the implied register operand.

#### Register Addressing

In register addressing, the instruction operand is a name or expression specifying an 8-bit register. The designated register contains the value on which the instruction operates. Any 8-bit register may be specified, except for the status register.

This is an efficient addressing mode: only three bits are needed to specify any given register. Another advantage of register addressing is that the speed of program execution is increased: registers reside within the processor itself, and thus instructions do not require external access of data.

#### Register Pair Addressing

Register pair addressing allows simple and direct manipulation of 16-bit quantities. In this addressing mode the instruction operand is a 16-bit register name or expression that evaluates to a legal register pair. The value operated on is the 16-bit quantity contained in the specified register pair.

12A-4 @

### Stack Addressing

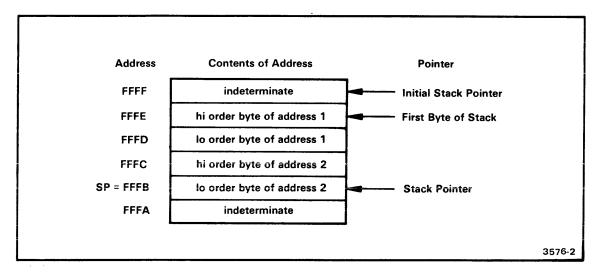

In stack addressing, a LIFO (last in-first out) stack growing downward in memory is referenced by any stack instruction, most commonly a POP or PUSH. The stack is normally initialized with a SPHL instruction which sets the value of the initial stack pointer (SP).

Fig. 12A-2. Stack Implementation.

The stack shown above has been initialized with the address FFFF as the value of the initial stack pointer. Two subsequent PUSH instructions have loaded addresses 1 and 2 onto the stack. Note that because the stack holds 16-bit quantities, the basic stack unit is two bytes stored in consecutive memory addresses. The high-order byte of this basic stack unit is stored at a higher address than the low-order byte. Note also that the stack pointer (SP) always points to a low-order byte.

### NOTATIONAL CONVENTIONS

The following list contains short descriptions of the symbols and abbreviations used in the specification of the instruction set.

(address) Contents of specified address.

((address)) Contents of address pointed to by specified address.

Separates number of cycles if condition not met, on left, from number if

condition met, on right.

= 0 The designated flag is cleared.

= 1 The designated flag is set.

Assignment of right argument to left argument.

A The 8-bit accumulator (a). Also the 16-bit PSW.

AC The Auxiliary Carry flag.

B The 16-bit **B** register pair. Also the 8-bit **b** register.

C The 8-bit c register.

clear To assign 0 to a flag value.

CY The Carry flag.

cycle A clock cycle.

D The 16-bit **D** register pair. Also the 8-bit **d** register.

destination The destination operand in a data transfer instruction.

devicenum The number (0-255) of an external device.

E The 8-bit e register.

H The 16-bit H register pair. Also the 8-bit h register.

immed16 A 16-bit immediate address, expression, or symbol.

immed8 An 8-bit immediate data byte, expression, or symbol.

L The 8-bit I register.

label A symbol or expression representing a 16-bit address.

M The memory byte indirectly addressed by the H register pair.

operand The general type of data object required by the instruction.

operand type A particular type of data object required by the instruction.

P The Parity flag.

PC The 16-bit Program Counter.

PSW The Program Status Word: the accumulator (a) and status register considered

as a 16-bit pseudo-register pair.

register An 8-bit register: a, b, c, d, e, h, or 1.

regpair A 16-bit register pair: B, D, or H.

regpairhi The high-order byte of a register pair.

regpairlo The low-order byte of a register pair.

S The Sign flag.

set To assign 1 to a flag value.

source The source operand in a data transfer instruction.

SP The 16-bit Stack Pointer.

status The 8-bit status register containing condition flags.

target An expression or label reducible to a 16-bit address.

vectornum Number (0-7) of restart vector.

Z The Zero flag.

### **Register Notation**

Wherever a register is specified in an operand field, a numeric argument may be given as well. In fact, all register names are treated as symbols and will appear in the symbol table of the assembler listing. Each register name is assigned the numeric value given in Table 12A-2. Note that this numeric argument may never exceed 7.

Table 12A-2

Register Numbering

| Register<br>Name | Numeric<br>Value |  |

|------------------|------------------|--|

| A                | 7                |  |

| В                | 0                |  |

| С                | 1                |  |

| D                | 2                |  |

| E                | 3                |  |

| Н                | 4                |  |

| L                | 5                |  |

| M                | 6                |  |

| PSW              | 6                |  |

| SP               | 6                |  |

| Mnemonic | Operands      | (Description)                |            |       | Flags<br>Affected |

|----------|---------------|------------------------------|------------|-------|-------------------|

|          |               |                              | Сус        | les   |                   |

|          | Operand Types | Bytes                        | A0808      | 8085A | Examples          |

| INSTRUC  | TION SET      |                              |            |       |                   |

|          | HON 3L1       |                              |            |       |                   |

| Jumps    |               |                              |            |       |                   |

| JMP      | target        | (Load the PC target address  |            |       | none              |

|          | label         | 3                            | 10         | 10    | JMP LOOP+5        |

| PCHL     | none          | (Load the PC contents of the |            | pair) | none              |

|          | _             | 1                            | 5          | 6     | PCHL              |

| JC       | target        | (Jump if carry               | set-CY=1   | )     | none              |

|          | label         | 3                            | 10         | 7/10  | JC LOOP+0FFH      |

| JNC      | target        | (Jump if carry CY=0)         | not set-   |       | none              |

|          | label         | 3                            | 10         | 7/10  | JNC 0FFFFH        |

| JZ       | target        | (Jump if zero                | set—Z=1)   |       | none              |

|          | label         | 3                            | 10         | 7/10  | ĴΖ (10+34)        |

| JNZ      | target        | (Jump if zero                | not set—Z= | =0)   | none              |

|          | label         | 3                            | 10         | 7/10  | JNZ SUM           |

| JP       | target        | (Jump if plus-               | -S=0)      |       | none              |

|          | label         | 3                            | 10         | 7/10  | JP POSRES         |

| JM       | target        | (Jump if minu                | s—S=1)     |       | none              |

|          | label         | 3                            | 10         | 7/10  | JM NEG            |

| JPE      | target        | (Jump if parity              | even—P=    | 1)    | none              |

|          | label         | 3                            | 10         | 7/10  | JPE EVEN          |

| JPO      | target        | (Jump if parity              | odd—P=0    | )     | none              |

|          | label         | 3                            | 10         | 7/10  | JPO ODD+5         |

| Mnemonic    | Operands        | (Description)                  |             |          | Flags<br>Affected  |

|-------------|-----------------|--------------------------------|-------------|----------|--------------------|

|             |                 |                                | Сус         | les      |                    |

|             | Operand Types   | Bytes                          | A0808       | 8085A    | Examples           |

|             |                 |                                |             |          |                    |

| Stack Opera | ations          |                                |             |          |                    |

| POP         | destination     | (regpairlo⊷(S<br>regpairhi⊷(Sl |             |          | none <sup>a</sup>  |

|             | regpair<br>PSW  | 1<br>1                         | 10<br>10    | 10<br>10 | POP B<br>POP PSW   |

| PUSH        | source          | (SP←SP−1, (S<br>SP←SP−1, (S    |             |          | none               |

|             | regpair<br>PSW  | 1<br>1                         | 11<br>11    | 12<br>12 | PUSH H<br>PUSH PSW |

| SPHL        | none            | (Load SP with register pair)   | h H         |          | none               |

|             |                 | 1                              | 5           | 6        | SPHL               |

| XTHL        | none            | (Exchange 16 top of stack v    |             |          | none               |

|             | _               | 1                              | 18          | 16       | XTHL               |

| Subroutine  | Handling: Calls |                                |             |          |                    |

| CALL        | target          | (Call subrout address, unc     |             |          | none               |

|             | label           | 3                              | 17          | 18       | CALLWRITENUM       |

| CC          | target          | (Call If carry                 | set—CY=1)   |          | none               |

|             | label           | 3                              | 11/17       | 9/18     | CC SUB1            |

| CNC         | target          | (Call if carry                 | not set—CY  | =0)      | none               |

|             | label           | 3                              | 11/17       | 9/18     | CNC SUB2           |

| CZ          | target          | (Call if zero                  | set—Z=1)    |          | none               |

|             | label           | 3                              | 11/17       | 9/18     | CZ SUBZ+5          |

| CNZ         | target          | (Call if zero ı                | not set—Z=0 | )        | none               |

|             | label           | 3                              | 11/17       | 9/18     | CNZ NOZEE          |

| CM          | target          | (Call if minus                 | s S=1)      |          | none               |

|             | label           | 3                              | 11/17       | 9/18     | CM NEG-4           |

| СР          | target          | (Call if plus-                 | -S=0)       |          | none               |

|             | label           | 3                              | 11/17       | 9/18     | CP SUBP            |

| Mnemonic   | Operands             | (Description)              |             |             | Flags<br>Affected |

|------------|----------------------|----------------------------|-------------|-------------|-------------------|

|            |                      |                            | Сус         | les         |                   |

|            | Operand Types        | Bytes                      | A0808       | 8085A       | Examples          |

|            |                      |                            |             |             |                   |

| Subroutine | Handling: Calls (con | t.)                        |             |             |                   |

| CPE        | target               | (Call if parity            | even—P=1)   |             | none              |

|            | label                | 3                          | 11/17       | 9/18        | CPE EVEN3         |

| СРО        | target               | (Call if parity            | odd—P=0)    |             | none              |

|            | label                | 3                          | 11/17       | 9/18        | CPO 345           |

|            |                      |                            |             |             |                   |

|            | Handling: Returns    | 450.                       | !4 !! - d   |             |                   |

| RET        | none                 | (Return from subroutine, u |             | lly)        | none              |

|            |                      | 1                          | 10          | 10          | RET               |

| RC         | none                 | (Return if car             | ry setCY=   | <b>:1</b> ) | none              |

|            | _                    | 1                          | 5/11        | 6/12        | RC                |

| RNC        | none                 | (Return if care            | ry not set— |             | none              |

|            |                      | 1                          | 5/11        | 6/12        | RNC               |

| RZ         | none                 | (Return if zer             | o set—Z=1)  |             | none              |

|            | modelmen             | 1                          | 5/11        | 6/12        | RZ                |

| RNZ        | none                 | (Return if zero            | o not set-  | ,           | none              |

|            |                      | 1                          | 5/11        | 6/12        | RNZ               |

| RM         | none                 | (Return if mir             | nus—S=1)    |             | none              |

|            |                      | 1                          | 5/11        | 6/12        | RM                |

| RP         | none                 | (Return if plu             | sS=0)       |             | none              |

|            | _                    | 1                          | 5/11        | 6/12        | RP                |

| RPE        | none                 | (Return if par             | ity even—P  | =1)         | none              |

|            |                      | 1                          | 5/11        | 6/12        | RPE               |

| RPO        | none                 | (Return if par             | ity odd—P=  | =0)         | none              |

|            | _                    | 1                          | 5/11        | 6/12        | RPO               |

| Mnemonic      | Operands                                                | (Description)                                       |              |             | Flags<br>Affected             |

|---------------|---------------------------------------------------------|-----------------------------------------------------|--------------|-------------|-------------------------------|

|               |                                                         |                                                     | Сус          | les         |                               |

|               | Operand Types                                           | Bytes                                               | 8080A        | 8085A       | Examples                      |

| Data Transfer |                                                         |                                                     |              |             |                               |

| MOV           | destination,<br>source                                  | (Copy source to                                     | o destinatio | on)         | none                          |

|               | register,register<br>register,memory<br>memory,register | 1<br>1<br>1                                         | 5<br>7<br>7  | 4<br>7<br>7 | MOV B,A<br>MOV E,M<br>MOV M,D |

| MVI           | destination,<br>source                                  | (Copy immedia destination)                          | te byte to   |             | none                          |

|               | register,immed8<br>memory,immed8                        | 2<br>2                                              | 7<br>10      | 7<br>10     | MVI D,255<br>MVI M,0FFH       |

| LDA           | source                                                  | (Load accumula contents of sou                      |              | s)          | none                          |

|               | label                                                   | 3                                                   | 13           | 13          | LDA 444Q                      |

| LHLD          | source                                                  | (Load I with by<br>Load h with by                   |              |             | none                          |

|               | label                                                   | 3                                                   | 16           | 16          | LHLD VAL                      |

| LDAX          | source                                                  | (Load accumula<br>contents addres<br>register pair) |              | ırce        | none                          |

|               | regpair <sup>b</sup>                                    | 1                                                   | 7            | 7           | LDAX D                        |

| LXI           | destination,<br>source                                  | (Load destination 16-bit immediated)                |              |             | none                          |

|               | regpair,immed16<br>SP,immed16                           | 3<br>3                                              | 10<br>10     | 10<br>10    | LXI B,0FA14H<br>LXI SP,NEWSP  |

| STA           | destination                                             | (Store contents accumulator at                      |              | )           | none                          |

|               | label                                                   | 3                                                   | 13           | 13          | STA BUFFER                    |

| SHLD          | destination                                             | (Store I at desti<br>Store h at desti               |              |             | none                          |

|               | label                                                   | 3                                                   | 16           | 16          | SHLD FROM+1                   |

12A-12

| Mnemonic     | Operands             | (Description)                                                 |               |            | Flags<br>Affected |

|--------------|----------------------|---------------------------------------------------------------|---------------|------------|-------------------|

|              |                      |                                                               | Сус           | les        |                   |

|              | Operand Types        | Bytes                                                         | A0808         | 8085A      | Examples          |

| <del>-</del> | _                    |                                                               |               |            |                   |

| Data Transfe | er (cont.)           |                                                               |               |            |                   |

| STAX         | destination          | (Store contents<br>accumulator at<br>address contain<br>pair) | t destination |            | none              |

|              | regpair <sup>ь</sup> | . 1                                                           | 7             | 7          | STAX B            |

| XCHG         | none                 | (Exchange cor<br>and D register                               |               |            | none              |

|              | <del></del>          | 1                                                             | 4             | 4          | XCHG              |

| Arithmetic O | perations            |                                                               |               |            |                   |

| ADD          | source               | (Add source to accumulator w                                  |               | <b>(</b> ) | CY,AC,S,Z,P       |

|              | register<br>memory   | 1<br>1                                                        | 4<br>7        | 4<br>7     | ADD B<br>ADD M    |

| ADC          | source               | (Add source to<br>accumulator w                               |               |            | CY,AC,S,Z,P       |

|              | register<br>memory   | 1<br>1                                                        | 4<br>7        | 4<br>7     | ADC E<br>ADC M    |

| ADI          | source               | (Add immediat                                                 |               | arry)      | CY,AC,S,Z,P       |

|              | immed8               | 2                                                             | 7             | 7          | ADI 34Q           |

| ACI          | source               | (Add immediat                                                 |               | )          | CY,AC,S,Z,P       |

|              | immed8               | 2                                                             | 7             | 7          | ACI 34H           |

| DAD          | source               | (Add contents register pair to                                |               | pair)      | CY                |

|              | regpair<br>SP        | 1<br>1                                                        | 10<br>10      | 10<br>10   | DAD H<br>DAD SP   |

| SUB          | source               | (Subtract sour                                                |               | borrow)    | CY°,AC,S,Z,P      |

|              | register<br>memory   | 1<br>1                                                        | 4<br>7        | 4<br>7     | SUB D<br>SUB M    |

| Mnemonic     | Operands           | (Description)                                                                                                |           |         | Flags<br>Affected |

|--------------|--------------------|--------------------------------------------------------------------------------------------------------------|-----------|---------|-------------------|

|              |                    |                                                                                                              | Cycles    |         |                   |

|              | Operand Types      | Bytes                                                                                                        | A0808     | 8085A   | Examples          |

|              |                    |                                                                                                              |           |         |                   |

| Arithmetic O | perations (cont.)  |                                                                                                              |           |         |                   |

| SBB          | source             | (Subtract sour                                                                                               |           | rrow)   | CY°,AC,S,Z,P      |

|              | register<br>memory | 1<br>1                                                                                                       | 4<br>7    | 4<br>7  | SBB C<br>SBB M    |

| SUI          | source             | (Subtract imm<br>source byte fr<br>with no borro                                                             | om accumu | lator   | CY°,AC,S,Z,P      |

|              | immed8             | 2                                                                                                            | 7         | 7       | SUI 255           |

| SBI          | source             | (Subtract immediate source byte from accumulator with borrow)                                                |           |         | CY°,AC,S,Z,P      |

|              | immed8             | 2                                                                                                            | 7         | 7       | SBI 251           |

| DAA          | none               | (Convert contents of accu-<br>mulator to BCD. Use immediately<br>after accumulator addition<br>or increment) |           |         | CY,AC,S,Z,P       |

|              |                    | 1                                                                                                            | 4         | 4       | DAA               |

| INR          | destination        | (Increment de<br>1, carry flag u                                                                             | •         |         | AC,S,Z,P          |

|              | register<br>memory | 1<br>1                                                                                                       | 5<br>10   | 4<br>10 | INR B<br>INR M    |

| INX          | destination        | (Increment de<br>register pair b                                                                             |           |         | none              |

|              | regpair<br>SP      | 1<br>1                                                                                                       | 5<br>5    | 6<br>6  | INX H<br>INX SP   |

| DCR          | destination        | (Decrement de<br>1, carry flag u                                                                             |           | y       | AC,S,Z,P          |

|              | register<br>memory | 1<br>1                                                                                                       | 5<br>10   | 4<br>10 | DCR E<br>DCR M    |

| DCX          | destination        | (Decrement de register pair b                                                                                |           |         | none              |

|              | regpair<br>SP      | 1<br>1                                                                                                       | 5<br>5    | 6<br>6  | DCX H<br>DCX SP   |

| Mnemonic     | Operands           | (Description)                                                 |                       |        | Flags<br>Affected              |

|--------------|--------------------|---------------------------------------------------------------|-----------------------|--------|--------------------------------|

|              |                    |                                                               | Cyc                   | es     |                                |

|              | Operand Types      | Bytes                                                         | 8080A                 | 8085A  | Examples                       |

|              |                    |                                                               |                       |        |                                |

| Logical Oper | rations            |                                                               |                       |        |                                |

| ANA          | source             | (AND source be contents of ac-                                |                       |        | CY=0,<br>AC <sup>d</sup> ,S,Z  |

|              | register<br>memory | 1<br>1                                                        | 4                     | 4<br>7 | ANA C<br>ANA M                 |

| ANI          | source             | (AND immedia<br>with contents (<br>accumulator)               | -                     |        | CY=0,<br>AC <sup>d</sup> ,S,Z, |

|              | immed8             | 2                                                             | 7                     | 7      | ANI 123                        |

| ORA          | source             | (OR source by contents of ac                                  |                       |        | CY=0, AC=0<br>S,Z,P            |

|              | register<br>memory | 1<br>1                                                        | 4<br>7                | 4<br>7 | ORA C<br>ORA M                 |

| ORI          | source             | (OR immediate contents of ac                                  |                       |        | CY=0, AC=0,<br>S,Z,P           |

|              | immed8             | 2                                                             | 7                     | 7      | QRI 10101010B                  |

| XRA          | source             | (XOR source to contents of ac                                 |                       |        | CY=0,AC=0,<br>S,Z,P            |

|              | register<br>memory | 1<br>1                                                        | 4<br>7                | 4<br>7 | XRA B<br>XRA M                 |

| XRI          | source             | (XOR immedia<br>with contents<br>accumulator)                 |                       |        | CY=0,AC=0,<br>S,Z,P            |

|              | immed8             | 2                                                             | 7                     | 7      | XRI 11010101B                  |

| CMA          | none               | (One's-comple<br>contents of ac                               |                       |        | none                           |

|              |                    | 1                                                             | 4                     | 4      | CMA                            |

| CMP          | source             | (Subtract sour accumulator, I stored. If sour then CY=1, else | esult not ce greater, |        | CY,AC,S,Z,P                    |

|              | register<br>memory | 1<br>1                                                        | 4<br>7                | 4<br>7 | CMP B<br>CMP M                 |

| Mnemonic | Operands        | (Description)                                           |                              |       | Flags<br>Affected |  |

|----------|-----------------|---------------------------------------------------------|------------------------------|-------|-------------------|--|

|          |                 | Cycles                                                  |                              |       |                   |  |

|          | Operand Types   | Bytes                                                   | A0808                        | 8085A | Examples          |  |

|          |                 |                                                         |                              |       |                   |  |

|          | rations (cont.) |                                                         |                              |       |                   |  |

| CPI      | source          | (Subtract imm from accumul not stored. If then CY=1, el | ator. Result<br>source great | ter,  | CY,AC,S,Z,P       |  |

|          | immed8          | 2                                                       | 7                            | 7     | CPI MASK-4        |  |

| STC      | none            | (Set carry flag                                         | to 1)                        |       | CY=1              |  |

|          | _               | 1                                                       | 4                            | 4     | STC               |  |

| CMC      | none            | (Complement                                             | carry flag)                  |       | CY                |  |

|          | _               | 1                                                       | 4                            | 4     | CMC               |  |

| RAR      | none            | (Rotate accun<br>through carry)                         |                              |       | СҮ                |  |

|          |                 | [c]                                                     | accumulat                    | or    |                   |  |

|          | _               | 1                                                       | 4                            | 4     | RAR               |  |

| RAL      | none            | (Rotate accum<br>through carry)                         |                              |       | CY                |  |

|          |                 | C                                                       | accumulate                   | or.   |                   |  |

|          |                 | 1                                                       | 4                            | 4     | RAL               |  |

| RRC      | none            | (Rotate accum carry affected)                           |                              | ,     | CY                |  |

|          |                 | С                                                       | accumulate                   | or    |                   |  |

|          | _               | 1                                                       | 4                            | 4     | RRC               |  |

| Mnemonic     | Operands            | (Description)                                                             |                    |           | Flags<br>Affected  |

|--------------|---------------------|---------------------------------------------------------------------------|--------------------|-----------|--------------------|

|              |                     |                                                                           | Cycl               | es        |                    |

|              | Operand Types       | Bytes                                                                     | 8080A              | 8085A     | Examples           |

| Logical Ope  | rations (cont.)     |                                                                           |                    |           |                    |

| RLC          | none                | (Rotate accumu<br>carry affected)                                         | ılator left,       |           | CY                 |

|              |                     | C                                                                         | accumulato         |           |                    |

|              | _                   | 1                                                                         | 4                  | 4         | RLC                |

| Miscellaneou | ıs (IN, OUT, HLT, N | OP, RST, Interrupt                                                        | t Instructio       | ns)       |                    |

| IN           | devicenum           | (Send byte to a lator from exter [0—255])                                 |                    |           | none               |

|              | immed8              | 1                                                                         | 10                 | 10        | IN 255             |

| OUT          | devicenum           | (Send contents lator to externa [0—255])                                  |                    | <b> -</b> | none               |

|              | immed8              | 1                                                                         | 10                 | 10        | OUT PRINTER        |

| HLT          | none                | (Stop execution processor)                                                | n of               |           | none               |

|              | _                   | 1                                                                         | 7                  | 5         | HLT                |

| NOP          | none<br>—           | (No operation)                                                            | 4                  | 4         | <b>none</b><br>NOP |

| RST          | vectornum           | (PUSH PC on s<br>high-order byte<br>with [00], load I<br>byte with [8 X v | of PC<br>low-order | )         | none               |

|              | immed8              | 1                                                                         | 11                 | 12        | RST 7              |

| EI           | none                | (Enable interrup<br>next instruction                                      |                    |           | none               |

|              | _                   | 1                                                                         | 4                  | 4         | EI                 |

| DI           | none                | (Disable interru next instruction                                         |                    |           | none               |

|              | _                   | . 1                                                                       | 4                  | 4         | DI                 |

| Mnemonic            | Operands                   | (Description)                            |        |       | Flags<br>Affected |

|---------------------|----------------------------|------------------------------------------|--------|-------|-------------------|

|                     |                            |                                          | Cycles |       |                   |

|                     | Operand Types              | Bytes                                    | 8080A  | 8085A | Examples          |

| Instructions<br>RIM | Available on 8085A<br>none | only<br>(Copy interrup<br>to accumulator |        |       | none              |

|                     | -                          | 1                                        | _      | 4     | RIM               |

| SIM                 | none                       | (Copy contents accumulator to mask)      |        |       | none              |

|                     |                            | 1                                        |        | 4     | SIM               |

<sup>&</sup>lt;sup>2</sup>POP PSW affects all flags since the low-order byte of the top stack unit is loaded into the status register.

12A-18

<sup>&</sup>lt;sup>b</sup>LDAX and STAX apply to B and D register pairs only: the H register pair is illegal.

<sup>&</sup>lt;sup>c</sup>Carry set to 1 if borrow required.

<sup>&</sup>lt;sup>d</sup>AC=1 for 8085A.

# **RESERVED WORDS**

The following names may **not** be used to represent an address, data item, or variable. They are words reserved for specifying instruction mnemonics, register names, and assembler directives, options, and operators.

### 8080A/8085A Mnemonics

| ACI  | CMC | DAD | JM   | LHLD | PUSH | RP   | SPHL |

|------|-----|-----|------|------|------|------|------|

| ADC  | CMP | DCR | JMP  | LXI  | RAL  | RPE  | STA  |

| ADD  | CNC | DCX | JNC  | MOV  | RAR  | RPO  | STAX |

| ADI  | CNZ | DÍ  | JNZ  | MVI  | RC   | RRC  | STC  |

| ANA  | CP  | EI  | JP   | NOP  | RET  | RST  | SUB  |

| ANI  | CPE | HLT | JPE  | ORA  | RIM  | RZ   | SUI  |

| CALL | CPI | IN  | JPO  | ORI  | RLC  | SBB  | XCHG |

| CC   | CPO | INR | JZ   | OUT  | RM   | SBI  | XRA  |

| CM   | CZ  | INX | LDA  | PCHL | RNC  | SHLD | XRI  |

| CMA  | DAA | JC  | LDAX | POP  | RNZ  | SIM  | XTHL |

# 8080A/8085A Register Names

| Α | В | С | D   | Ε  |

|---|---|---|-----|----|

| Н | L | М | PSW | SP |

# Tektronix Assembler Directives, Options, and Operators

| ABSOLUTE | END     | INPAGE | PAGE    | STITLE  |

|----------|---------|--------|---------|---------|

| ASCII    | ENDIF   | LIST   | REPEAT  | STRING  |

| BASE     | ENDM    | LO     | RESERVE | SYM     |

| BLOCK    | ENDOF   | MACRO  | RESUME  | TITLE   |

| BYTE     | ENDR    | ME     | SCALAR  | TRM     |

| CND      | EQU     | MEG    | SECTION | WARNING |

| COMMON   | EXITM   | MOD    | SEG     | WORD    |

| CON      | GLOBAL  | NAME   | SET     |         |

| DBG      | HI      | NCHR   | SHL     |         |

| DEF      | !F      | NOLIST | SHR     |         |

| ELSE     | INCLUDE | ORG    | SPACE   |         |

# PAGE SIZE

The page size of the 8080A/8085A Assembler is 256 bytes.

## **ERROR MESSAGES**

The following error messages are specific to the 8080A and 8085A microprocessors:

- \*\*\*\*\* ERROR: 251 Missing or invalid operand. Either a syntax error has occurred in an operand or the operand has been omitted.

- \*\*\*\*\* ERROR: 252 Register expression greater than 7. A register designation expression exceeds the number 7 and thus does not specify a legal register. Refer back to the Notational Conventions in this section for a discussion of register notation.

- \*\*\*\*\* ERROR: 253 Invalid register pair. A register designation expression is either odd, greater than 6, or illegal for the particular instruction. Note that all register pairs must be specified by an even numeric argument. Refer back to the Notational Conventions in this section for a discussion of register notation.

- \*\*\*\*\* ERROR: 254 Register expression is not scalar. An address expression is used where a register expression is required. Refer back to the Notational Conventions in this section for a discussion of register notation.

# **IRREGULARITIES**

### Differences Between The 8080A and the 8085A

The 8085A supports features unavailable on the 8080A: the RIM and SIM instructions, and an interrupt mask with three additional restart vectors. The 8085A and 8080A also implement the ANA and ANI instructions differently. The 8085A sets the auxiliary carry flag to one for both instructions. On the 8080A, the auxiliary carry flag is assigned the value resulting from a logical OR of bit 3 of the accumulator and bit 3 of the source byte.

Timing differences between the 8080A and 8085A are documented with the description of each instruction.

**12A-20** @

### MANUAL CHANGE INFORMATION

At Tektronix, we continually strive to keep up with latest electronic developments by adding circuit and component improvements to our instruments as soon as they are developed and tested.

Sometimes, due to printing and shipping requirements, we can't get these changes immediately into printed manuals. Hence, your manual may contain new change information on following pages.

A single change may affect several sections. Since the change information sheets are carried in the manual until all changes are permanently entered, some duplication may occur. If no such change pages appear following this page, your manual is correct as printed.

# **MANUAL CHANGE INFORMATION**

Date: 11-15-80 Change Reference: C1/1180

Product: 8550: 8080A/8085A ASSEMBLER SPECIFICS Manual Part No.: 070-3576-00

#### **DESCRIPTION**

TEXT CORRECTION

Page 12A-1

In Table 12A-1, the high-order byte of the D register pair should be "d", and the low-order byte should be "e". Change the third line of the table to read as follows:

D Register Pair d e

# **Tektronix**

# MANUAL CHANGE INFORMATION

COMMITTED TO EXCELLENCE Date: 3-23-81 Change Reference: C10/381

Product: GENERAL LIMITED RIGHTS LEGEND Manual Part No.: GENERAL

#### DESCRIPTION

### LIMITED RIGHTS LEGEND

| Software Licens | No | <br> |  |

|-----------------|----|------|--|

|                 |    |      |  |

Contractor: Tektronix, Inc.

Explanation of Limited Rights Data Identification Method

Used: Entire document subject to limited rights.

Those portions of this technical data indicated as limited rights data shall not, without the written permission of the above Tektronix, be either (a) used, released or disclosed in whole or in part outside the Customer, (b) used in whole or in part by the Customer for manufacture or, in the case of computer software documentation, for preparing the same or similar computer software, or (c) used by a party other than the Customer, except for: (i) emergency repair or overhaul work only, by or for the Customer, where the item or process concerned is not otherwise reasonably available to enable timely performance of the work, provided that the release or disclosure hereof outside the Customer shall be made subject to a prohibition against further use, release or disclosure; or (ii) release to a foreign government, as the interest of the United States may require, only for information or evaluation within such government or for emergency repair or overhaul work by or for such government under the conditions of (i) above. This legend, together with the indications of the portions of this data which are subject to such limitations shall be included on any reproduction hereof which includes any part of the portions subject to such limitations.

#### RESTRICTED RIGHTS IN SOFTWARE

The software described in this document is licensed software and subject to restricted rights. The software may be used with the computer for which or with which it was acquired. The software may be used with a backup computer if the computer for which or with which it was acquired is inoperative. The software may be copied for archive or backup purposes. The software may be modified or combined with other software, subject to the provision that those portions of the derivative software incorporating restricted rights software are subject to the same restricted rights.

Copyright © 1980 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and are registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

# **MANUAL CHANGE INFORMATION**

Date: <u>5/31/83</u> Change Reference: <u>C2/683</u>

Product: 8550: 8080A/8085A Assembler Specifics Manual Part No.: 070-3576-00

DESCRIPTION

Product Group 61

CHANGE INSTRUCTIONS

THIS IS A PAGE REPLACEMENT CHANGE.

To implement this change:

- a. Remove old title page.

- b. Insert new title page.

Part No. 070-3576-00 Product Group 61

8550 Microcomputer Development Lab

Assembler Specifics

8080A/8085A

This manual supports the following TEKTRONIX products:

ASM8085

Option 1Z

This manual supports a software module that is compatible with:

DOS 50 Version 1 (8550) DOS 50 Version 2 (8550)

Please check for change information at the rear of this manual

#### LIMITED RIGHTS LEGEND

| Software License No |  |

|---------------------|--|

|---------------------|--|

Contractor: Tektronix, Inc.

Explanation of Limited Rights Data Identification Method

Used: Entire document subject to limited rights.

Those portions of this technical data indicated as limited rights data shall not, without the written permission of the above Tektronix, be either (a) used, released or disclosed in whole or in part outside the Customer, (b) used in whole or in part by the Customer for manufacture or, in the case of computer software documentation, for preparing the same or similar computer software, or (c) used by a party other than the Customer, except for: (i) emergency repair or overhaul work only, by or for the Customer, where the item or process concerned is not otherwise reasonably available to enable timely performance of the work, provided that the release or disclosure hereof outside the Customer shall be made subject to a prohibition against further use, release or disclosure; or (ii) release to a foreign government, as the interest of the United States may require, only for information or evaluation within such government or for emergency repair or overhaul work by or for such government under the conditions of (i) above. This legend, together with the indications of the portions of this data which are subject to such limitations shall be included on any reproduction hereof which includes any part of the portions subject to such limitations.

#### RESTRICTED RIGHTS IN SOFTWARE

The software described in this document is licensed software and subject to **restricted rights**. The software may be used with the computer for which or with which it was acquired. The software may be used with a backup computer if the computer for which or with which it was acquired is inoperative. The software may be copied for archive or backup purposes. The software may be modified or combined with other software, subject to the provision that those portions of the derivative software incorporating restricted rights software are subject to the same restricted rights.

Copyright © 1980 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and are registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.